red PIs and consists of a s and some-

y the stimucted output. of 10 MHz), eginning of luction test. IC, one at a ge the probest program

If the fault PIs of the we have an e faults are I according

(14.1)

5, after the lose to 100 level? elationship circle with experimenn adopting being engi-

There are several algorithms for fault simulation: serial fault simulation, parallel fault simulation, and concurrent fault simulation. Next, we shall discuss each of these types of fault simulation in turn.

#### 14.4.1 Serial Fault Simulation

Serial fault simulation is the simplest fault-simulation algorithm. We simulate two copies of the circuit, the first copy is a good circuit. We then pick a fault and insert it into the faulty circuit. In test terminology, the circuits are called machines, so the two copies are a good machine and a faulty machine. We shall continue to use the term circuit here to show the similarity between logic and fault simulation (the simulators are often the same program used in different modes). We then repeat the process, simulating one faulty circuit at a time. Serial simulation is slow and is impractical for large ASICs.

#### 14.4.2 Parallel Fault Simulation

Parallel fault simulation takes advantage of multiple bits of the words in computer memory. In the simplest case we need only one bit to represent either a '1' or '0' for each node in the circuit. In a computer that uses a 32-bit word memory we can simulate a set of 32 copies of the circuit at the same time. One copy is the good circuit, and we insert different faults into the other copies. When we need to perform a logic operation, to model an AND gate for example, we can perform the operation across all bits in the word simultaneously. In this case, using one bit per node on a 32-bit machine, we would expect parallel fault simulation to be about 32 times faster than serial simulation. The number of bits per node that we need in order to simulate each circuit depends on the number of states in the logic system we are using. Thus, if we use a four-state system with '1', '0', 'X' (unknown), and 'z' (high-impedance) states, we need two bits per node.

Parallel fault simulation is not quite as fast as our simple prediction because we have to simulate all the circuits in parallel until the last fault in the current set is detected. If we use serial simulation we can stop as soon as a fault is detected and then start another fault simulation. Parallel fault simulation is faster than serial fault simulation but not as fast as concurrent fault simulation. It is also difficult to include behavioral models using parallel fault simulation.

#### 14.4.3 Concurrent Fault Simulation

Concurrent fault simulation is the most widely used fault-simulation algorithm and takes advantage of the fact that a fault does not affect the whole circuit. Thus we do not need to simulate the whole circuit for each new fault. In concurrent simulation we first completely simulate the good circuit. We then inject a fault and resimulate a copy of only that part of the circuit that behaves differently (this is the diverged circuit). For example, if the fault is in an inverter that is at a primary out-

Keeping track of exactly which parts of the circuit need to be diverged for each new fault is complicated, but the savings in memory and processing that result allow hundreds of faults to be simulated concurrently. Concurrent simulation is split into several chunks, you can usually control how many faults (usually around 100) are simulated in each chunk or pass. Each pass thus consists of a series of test cycles. Every circuit has a unique fault-activity signature that governs the divergence that occurs with different test vectors. Thus every circuit has a different optimum setting for faults per pass. Too few faults per pass will not use resources efficiently. Too many faults per pass will overflow the memory.

#### 14.4.4 Nondeterministic Fault Simulation

Serial, parallel, and concurrent fault-simulation algorithms are forms of deterministic fault simulation. In each of these algorithms we use a set of test vectors to simulate a circuit and discover which faults we can detect. If the fault coverage is inadequate, we modify the test vectors and repeat the fault simulation. This is a very time-consuming process.

As an alternative we give up trying to simulate every possible fault and instead, using **probabilistic fault simulation**, we simulate a subset or sample of the faults and extrapolate fault coverage from the sample.

In statistical fault simulation we perform a fault-free simulation and use the results to predict fault coverage. This is done by computing measures of observability and controllability at every node.

We know that a node is not stuck if we can make the node toggle—that is, change from a '0' to '1' or vice versa. A toggle test checks which nodes toggle as a result of applying test vectors and gives a statistical estimate of vector quality, a measure of faults detected per test vector. There is a strong correlation between high-quality test vectors, the vectors that will detect most faults, and the test vectors that have the highest toggle coverage. Testing for nodes toggling simply requires a single logic simulation that is much faster than complete fault simulation.

We can obtain a considerable improvement in fault simulation speed by putting the high-quality test vectors at the beginning of the simulation. The sooner we can detect faults and eliminate them from having to be considered in each simulation, the faster the simulation will progress. We take the same approach when running a production test and initially order the test vectors by their contribution to fault coverage. This assumes that all faults are equally likely. Test engineers can then modify the test program if they discover vectors late in the test program that are efficient in detecting faulty chips.

#### 14.4.5 Fault-Simulation Results

The output of a fault simulator separates faults into several fault categories. If we can detect a fault at a location, it is a testable fault. A testable fault must be placed

on a contr '0' to '1 net, so that ble nets at faults unte If a PC detected fa

detected fa fault). If the undetected PO of the fault detected fault

If the I circuit remands subset of possible faults separately sequence of threshold a soft-detectifult drop; the more like

A redu combination between log produce co stuck-at fau

If a fau occur withi fault that at Fault simulof computaonly to disc RS flip-flop fault catego

#### 14.4.6

In addition the number tem used by simulator us 'x'. Table 1 lations.

### Timing Controls.

- Lo Tirming controls poorides a way to specify the simulation time at which procedural statements will execute.

- 1). delay-based tirring control (delay control)

- 2). event-based timing control (event-control)

- 3). Level-sensitive timing control (condition). '). Delay-based.

- Los Delay-based terming control in an expression specifies the time duration blu when the statement is encountered and when it is executed.

- Lo delays are specified by the symbol#.

- y. inter-statement-

- 2). intra-staternent

- 3). Zero delay [explicit zero delay]

### Zero delay control.

Ly It is a method to ensure that a statement is executed last, ofter all other statements in that Simulation time are executed.

La This is used to chimnate race conditions.

L) Exi

initial x=0; end initial begin #0 x=1;

end

// zero delay.

executed last. (For at the end of fine o.

In the order in which x=1 & y=1 ase executed is not deterministic.

Note: \* The practice of assigning two different values to a variable in a single time step is generally not recommended and may case course race conditions in the design. # #0 provides a meful mechanism to control the order of execution of statements in a simulation.

### Event-based Timing control

- Los An event is the change in the value on a registers or a net.

- > Events can be utilized to trigger execution of a statement or a block of statements.

- s four types of event control.

- 1). regular event control (edge-toigged)

- 2). named event control

3). event or control

4). level-sensitive timing control

The Lord is my shepherd

I shall not lack anything. ps:23:1

### Behavioral style -> process flow

\* The behavior of a design is described using procedural constructs.

\* These ase

\* These as

- (i) Initial statement: executer only once.

(ii) Always statement: always executes in a boop, (ie) the statement is executed

- repeatedly.

- \* only a register data type can be assigned a value in either of there statements.

\* Register data type retourns its value until a

- neu value is adsigned.

- \* All initial statements and always statements.

begin execution at time o concurrently.

the the state of t

And the second s The state of the s

c character.

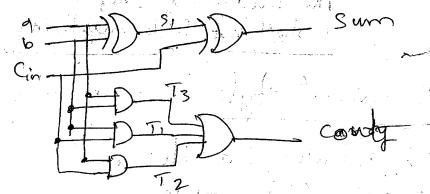

module FA-Seq (A, B, Cin, Sum, Cout); input A, B, Cin; output sum, Cout; reg Sum, Cout; reg T, Tz, Tz;

always

Sum = (A B) Cin;

Ti = 8 & Cin;

T2 = a & Gin;

T3 = a 2 b;

Cont = (T, 1 T2) 1 T3;

endmodule

Note: \* sum, cout, T, , Tz, Tz use ensigned values vitain always statement, so these ase declared to be seg dater type.

\* The always statement her segmential block (begin - end pair) associated with on event control (the expression following the @ character.

Association b) N sequiblock e entent control @ Lo whenever an event occurs on A, B, or Cin the sequential block is executed. Lo statements within a sequential block executes sequentially & the execution suspends after the last statement in the sequential block has executed. Ly After the sequential block completes execution, the always statement again vaits for on event to occur on A, B, or Cin. Lo The statements that appear within the Sequential block are examples of blocking procedural assignments. Is the blocking poocedwal assignments Completes execution before the next statement executes. Los A poocedural onsignment may optionally have a delay. (1) Inter-statement delay (ii) Intra-statement delay.

Inter-statement Delay:

Ly The delay by which a statement's execution is delayed.

Ly Ex! Sum = (A^B)^Cin;

#4Ti = A & Cin;

Ly The delay in the 2nd statement specifies that the execution of the

Specifies that the execution of the assignment is to be delayed by 4 time units. and then executes the second assignment.

Intra-segment-delay.

I, the delay b/w computing the value of the right-hand side expression and is assignment to the be left-hand.

Side.

Ex: Sum = #3 (AAB) Cin;

Listhe delay in this assignment means

that the value of the RHS expression

is to be computed first wait for

3 time units, and then assign the value to the sum.

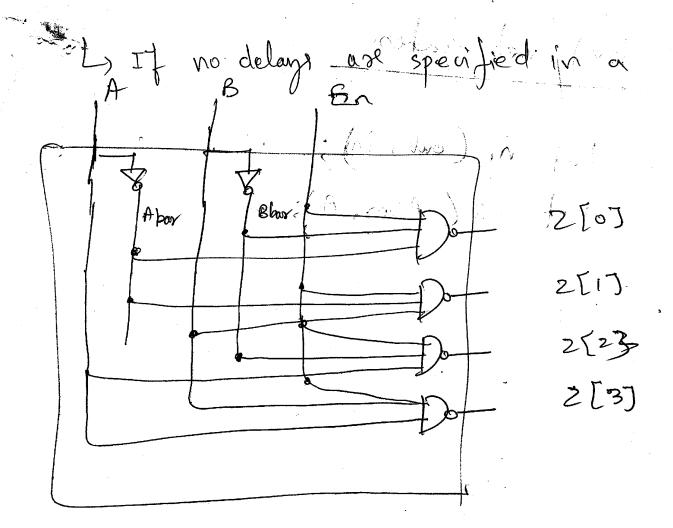

module decoder 2×4 (A, B, En, Z);

input A, B, En;

output [0:3]2;

vise Abour, Blow;

arsign #1 Abour = ~A;

arsign #1 Blowr = ~B;

arsign #2 2[0] = ~ (Abour 2 Blows En);

arsign #2 2[1] = ~ (Abour 2 Blows En);

arsign #2 2[1] = ~ (A & B & En);

arsign #2 2[2] = ~ (A & B & En);

arsign #2 2[3] = ~ (A & B & En);

entrodul

but not gates,

but no (out, in);

not no (Abur, A);

# The Lord is my shapherd I shall not lack anything. Ps: 23:1

### Initial statement

L) It executes only once.

It executes begins its execution at stast of simulation which is at time o.

Lis the styntax for the initial statement is:

[timing\_control] procedural\_statement-

procedural statement can be one of the following. Statements.

procedural\_assignment (blocking or non-blocking)

procedural\_continuous\_assignment

Conditional\_statement

case statement

loop\_statement

wait\_statement

disable\_statement

event\_toigger

Sequential\_block

parallel\_block

task\_enable (user or system)

- Lo The sequential block is the most. Commonly used procedural statement.

[begin. - end]

- 1) The timing control can be a

- y delay control: want for a cestain

- 2). event control: wail for an event to occur or

- 3) condition to become toue.

- Los The execution of an initial Statementcauses the procedural Statement to execute once.

- Lo The initial statement starts execution at time o.

fix:

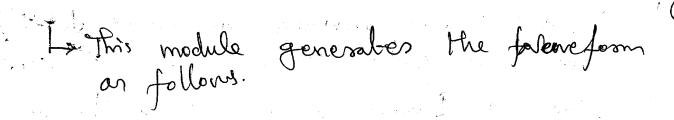

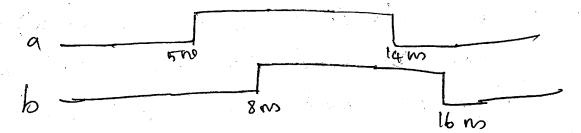

I timescale INS/Ins

Module Test (a, b);

output a, b;

reg a, b;

initial

begin

a= 0;

b=0;

end

a= #51;

b=#31;

a = #60; b = #20;end

endmodule.

Is The initial statement contains a sequential block which stasts execution at time Ons and after it completes executing all statements within the Sequential block, the initial statement statement Suspends forever.

Los In example, the sequential block contains blocking procedural assignments with intra-statement delays specified.

Mixed-design style:

La Within a module estautural and behavioral constauts can be mixed freely.

A module can contain a mixture of gate instantiations, module instantiations. Continuous assignments & always e initial statements amongst others.

Lo Values from always and foritial statements can drive gates or smitches. La values from gates vos conitinuous assignments (can only drive nets) can in turn be used to trigger always Statements and initial statements. module FA\_mix (A,B, Cin, Sum, Cout); input A, B, Cin; output sum, cout; reg cont; deg T, T2, T3; Crafe instantiation 208 XI(SI, A, B); always ... ( always statement @ (A or B or Cin) begin Ti = A& Cin; Tz= B & Cin T3 = A & B; Cont =  $(T_1 | T_2) | T_3$ ; end anstign Som = S, 1 Zin; // Continuous Assigned Endmodule

## Regular event control

Lo @ symbol is used to specify an event contain in signal value or at tre or -ve transition of the signal value.

dies is arraigned to good tre edge

$$2\rightarrow 1$$

data\_buf = of data\_pkt[0], data\_pkt[1], data-pkt[2], data-pkt[3]];

## Event OR control.

Ls A transition on any one of multiple Signals are events can trigger the execution of a statement or a block of statements.

Lis This is expressed as an OR of events or signals.

Is the hist-of events or signals expressed as an OR is also known as a sensitivity

Lo the keyword or is used to specify.

multiple triggers

fou!

always @ ( seset or clock or d).

begin

if ( reset)

g=11bo;

else if Cclock)

end. 9=d;

# Level - Sensitive Tiraing Control. Ly the ability to wait for a certain condition to be true before a statement or to black of statements is executed. 1) The keyword wait is used for level-sensitive constants. wait (count enable) #20 count=count+1 Les count enable is morrisoned continuously. \*\* If count enable is of the statement is not executed. # If itis logical, the statement count-county is executed after 20 time and Conditional statements. Lo used for making decisions based a upon constain conditions.

passed a upon certain contents.

Is used to decide whether or not a statement should be executed by executed to keyword if and else as used for conditional statements.

Syntone. Tit (expression) statement; 14 (exp) Statement; lebre statementz; if (expi) statement 1; espe if (eap2) etalement-2; Obe if (esp3) statem3; else drofant-statement. procedural assignments. I supdate values of reg, integer, real or time variables. Lothe value placed on a variable will remain unchanged until another procedural assignment updates the variable with a different value. Is not tike continuous assignment The value of net is continuously placed.

Two types: 10. Blocking assignment 20 mon-Blocking assignment Blocking. Los Blocking assignment statements are executed in the order they are specified in a sequential block. 1) There statements will not black execution of statements that Follow in a pasallel block. I The operator = is used. seg 2, y, 2 reg [15:0] reg-a, reg-b; initial integer count; beign=0; y=1; 2=1; count=0; rega = 16'bo; reg\_b= reg\_a; #15 deg-a[2]= 1/61

Non-blocking. is It allow scheduling of assignments without blocking execution of the Statements that follow in a sequential block. Ls A <= operators is used to Sperify non-blocking assignments. reg x, y, z reg [15:0] reg-a, reg-b; begin x=0; y=1; 2=1; Count = 0; reg-a = 16/60; reg-b=reg-a; reg-a[2] <= #15/61; reg-b[15:13] <= #10{x,y,23; Coontra Count +1;

Initial statement.

- \* syntax:

- \* Timing control : delay, event, conditions.

- \* protedural statements.

DAFF

module DFF (d, elk, q);

input d;

input dk;

output q;

reg q;

always @ (posedge dk)

9=d;

endmodule

lelay control.

is a method to ensure that a stement is executed last, ofter

Zeno

Ly It

11 FCF-17

### St. Joseph's College of Engineering Department of ECE

#### EC1401: VLSI DESIGN Question Bank

|    | PART-A                                                                              |

|----|-------------------------------------------------------------------------------------|

|    | UNIT-I                                                                              |

| 1  | What are the materials used for masks in IC technology?                             |

| _2 | What are the advantages of twin tub process?                                        |

| _3 | What are the advantages of EBL pattern generation?                                  |

| 4  | What are the types of oxidation?                                                    |

| 5  | What are the types of etching process?                                              |

| 6  | What are the advantages of SOI CMOS process?                                        |

| 7  | What is a thinox?                                                                   |

| 8  | How is the channel stop implant made?                                               |

| 9  | What are the types of interconnect?                                                 |

| 10 | What is BiCMOS?                                                                     |

| 11 | What is latch-up?                                                                   |

| 12 | List the two techniques that can be used to prevent latch-up.                       |

| 13 | What is guard ring?                                                                 |

| 14 | How is a capacitor created in CMOS fabrication process?                             |

| 15 | How is a resistor created in CMOS fabrication process?                              |

| 16 | What is the objective of the layout rules?                                          |

| 17 | What are the types of layout design rules?                                          |

| 18 | What is scribe line?                                                                |

| 19 | What is passivation or overglass?                                                   |

| 20 | List the four main CMOS technologies.                                               |

| 21 | Draw the circuit of a CMOS 2-input NAND gate.                                       |

| 22 | Distinguish electrically alterable and non-electrically alterable ROM.              |

| 23 | List the sequence of steps to create the physical layout of an inverter.            |

| 24 | Draw the physical layout of 2-input NOR gate                                        |

| 25 | What is Lambda-Based design rule?                                                   |

|    | UNIT-II                                                                             |

| 1  | Draw the structure of a nmos enhancement transistor.                                |

| 2  | Draw the characteristics of a n- channel & p – channel enhancement transistor.      |

| 3  | What are the advantages of SiO <sub>2</sub> as a dielectric?                        |

| 4  | State the parameters on which threshold voltage is dependent on.                    |

| 5  | What is a field induced junction?                                                   |

| 6  | What are the factors that influence the drain current.                              |

| 7  | Define cut – off and saturated regions in the characteristics of an MOS transistor. |

| 8  | Define threshold voltage                                                            |

| 9               | Define Body effect.                                                                         |

|-----------------|---------------------------------------------------------------------------------------------|

| $\frac{10}{10}$ | What is channel length modulation?                                                          |

| 11              | Draw the small signal model of a MOS transistor.                                            |

| 12              | Define noise margin. Illustrate how it can be obtained from the transfer characteristics of |

| 1 2             | a CMOS Inverter.                                                                            |

| 13              | What is a transmission gate.                                                                |

| 14              | Why is the transmission of logic 1 degraded as it passes through a nmos pass transistor.    |

| 15              | Why is the transmission of logic 0 degraded as it passes through a pmos pass transistor?    |

| 16              | Draw the structure & symbol of a CMOS tri - state inverter.                                 |

| 17              | Write the equation for total power dissipation.                                             |

| 18              | Define rise time (t <sub>r</sub> ).                                                         |

| 19              | Define fall time (t <sub>f</sub> )                                                          |

| 20              | Define delay time (t <sub>d</sub> ).                                                        |

| 21              | Compare NMOS & PMOS devices                                                                 |

| 22              | Compare enhancement and depletion mode devices.                                             |

| 23              | What is static power dissipation?                                                           |

| 24              | What is dynamic power dissipation?                                                          |

| 25              | List three modes of MOS transistor.                                                         |

|                 | UNIT-III                                                                                    |

| 1               | What is meant by continuous assignment statement in Verilog HDL?                            |

| 2               | List out different data types in verilog.                                                   |

| 3               | What are the types of modeling in verilog?                                                  |

| 4               | What is HDL? Name two types of HDLs.                                                        |

| 5               | What is Module?                                                                             |

| 6               | What is a task in Verilog?                                                                  |

| 7               | What is the key difference between an initial statement and an always statement?            |

| 8               | List any two capabilities of Verilog.                                                       |

| 9               | What is value set?                                                                          |

| 10              | Define net.                                                                                 |

| 11              | What is UDP?                                                                                |

| 12              | What are the types of event control?                                                        |

| 13              | Define an identifier                                                                        |

| 14              | Define a port. How is it declared?                                                          |

| 15              | What are the types of structural modeling?                                                  |

| 16              | List the types of Gate delay.                                                               |

| 17              | What are the types of procedural assignment?                                                |

| 18              | What is the difference between reduction operator and bitwise operator?                     |

| 19              | What is inter-statement delay?                                                              |

| 20              | What is intra-statement delay?                                                              |

| 21              | Give the structural coding of an Half adder.                                                |

| 22              | Give the behavioral coding of 2-input AND gate.                                             |

| 23              | Give the symbol, Truth table and syntax of bufit1.                                          |

| 24              | Write the syntax for gate primitive instantiation.                                          |

| 25              | What is replication operator?                                                               |

|                 | UNIT-IV                                                                                     |

| 1        | Draw the symbols of N & P – switches                                                   |

|----------|----------------------------------------------------------------------------------------|

| 2        | What is a crowbarred state?                                                            |

| 3        | Draw a CMOS NAND gate with its pull – up & pull – down Truth table.                    |

| 4        | Draw the symbol of a 2 i/p CMOS Mux.                                                   |

| 5        | Draw a CMOS positive level sensitive D latch.                                          |

| 6        | What is 22V10?                                                                         |

| 7        | What is CLB?                                                                           |

| 8        | When is a full custom ASIC designed?                                                   |

| 9        | What is a wafer lot?                                                                   |

| 10       | What is a mega cell?                                                                   |

| 11       | What is a gate array?                                                                  |

| 12       | What are the types of Masked gate arrays                                               |

| 13       | List the features of Channeled gate array. Channelless gate array, and Structured gate |

|          | array.                                                                                 |

| 14       | List the features of PLD.                                                              |

| 15       | What are the types of PLD's?                                                           |

| 16       | What are the Essential features of FPGA?                                               |

| 17       | What FAMOS?                                                                            |

| 18       | What is the difference between Full-custom ASIC and semi-custom ASIC?                  |

| 19       | What is the difference between CBIC and MGA?                                           |

|          | What is SOG?                                                                           |

| 21       | What is Antifuse?                                                                      |

| 22       | What is PLICE?                                                                         |

| 23       | What is ViaLink?                                                                       |

| 24       | What is the disadvantage of Embedded Gate Array                                        |

| 25       | Mention the characteristics of 22V10                                                   |

|          | UNIT-V                                                                                 |

| ]        | List some typical defects in the manufacturing of IC.                                  |

| 2        | What are SA0 & SA1 faults?                                                             |

| 3        | Define observability and controllability.                                              |

| 4        | what is fault sampling?                                                                |

| 5        | What is a sensitized path?                                                             |

| 6        | What are primary i/p's and o/p's?                                                      |

| 7        | State the 3 types of fault simulation process.                                         |

| 8        | What is delay fault testing?                                                           |

| 9        | What is ILA testing?                                                                   |

| 10       | What are the advantages & disadvantages of IDDQ?                                       |

| 11       | What are the various connections of a Test Access Port.? (TAP).                        |

| 12       | Describe the test architecture of a boundary scan using TAP.                           |

| 13       | What is a TAP controller?                                                              |

| 14<br>15 | Explain BYPASS ,EXTEST, SAMPLE /PRELOAD.  What is a test DR?                           |

| 16       |                                                                                        |

| 17       | What are boundary scan registers?                                                      |

| 18       | What is short circuit and open circuit faults?                                         |

| 10       | What is JTAG?                                                                          |

| 19 | What is Fault coverage?                                                               |

|----|---------------------------------------------------------------------------------------|

| 20 | Expand ATPG & SCOAP                                                                   |

| 21 | How are sequential faults caused in CMOS?                                             |

| 22 | What is BIST?                                                                         |

| 23 | What is LSSD?                                                                         |

| 24 | What is concurrent simulation?                                                        |

| 25 | List the three approaches of Design for testability                                   |

|    | PART-B                                                                                |

|    | UNIT-I                                                                                |

| 1  | (i) Draw and explain the n-well process (10)                                          |

|    | (ii) Explain the twin tub process with a neat diagram.(6)                             |

| 2  | Explain the various steps involved in p-well CMOS fabrication with necessary diagrams |

|    | (16)                                                                                  |

| 3  | Explain the terms (16)                                                                |

|    | (a) Oxidation                                                                         |

|    | (b) Epitaxy                                                                           |

|    | (c) Ion implantation                                                                  |

|    | (d) Diffusion                                                                         |

| 4  | (i) Explain SOI process in detail. (10)                                               |

|    | (ii) What are the advantages of SOI process? (6)                                      |

| 5  | (i) What is interconnect? Explain different types of interconnect. (8)                |

|    | (ii) Explain the fabrication of circuit elements in detail. (8)                       |

| 6  | (i) Discuss the origin of latch-up problems in CMOS circuits with necessary           |

|    | diagrams. Explain the remedial measures.(10)                                          |

| 7  | (ii) Draw and explain briefly the n-well CMOS design rules. (6)                       |

| /  | Explain a sequence of steps to create the physical layout of an inverter, NAND & NOR  |

| 8  | gates with neat diagram.(16)                                                          |

| 9  | Explain Layout design rules. (16) Write notes on                                      |

| 7  | (i) Design rule Backgrounder(6)                                                       |

|    | (ii) CAD tool sets(5)                                                                 |

|    | (iii)Design Hierarchy(5)                                                              |

| 10 | (i) What is latch-up & how is it triggered?                                           |

| •• | (ii) State & Explain the condition for prevention of latch-up.                        |

|    | UNIT-II                                                                               |

| 1  | Explain the operation of NMOS enhancement MOSFET with neat characteristics curves.    |

| _  | (16)                                                                                  |

| 2  | Explain the CMOS inverter DC characteristics.(16)                                     |

| 3  | Write notes on (i) The transmission gate. (8)                                         |

|    | (ii) Noise margin for a CMOS Inverter. (8)                                            |

| 4  | Derive the expression for the fall time and rise time of a CMOS inverter. (16)        |

| 5  | Explain the operation of PMOS enhancement MOSFET with neat characteristics curves.    |

|    | (16)                                                                                  |

| 6  | (i) Explain body effect. (6)                                                          |

|    | (ii) Derive the expression for threshold voltage for nMOS transistor                  |

|    |                                                                                       |

| 7        | Derive t                                      | he DC equations for a NMOS transistor (10).                                                          |

|----------|-----------------------------------------------|------------------------------------------------------------------------------------------------------|

| 8        | (i)                                           | Discuss the small signal model of an MOS transistor .(8)                                             |

|          | (ii)                                          | Explain Static power dissipation in a CMOS inverter(8)                                               |

| 9        | Explain                                       | power dissipation in a CMOS inverter. (16)                                                           |

| 10       | Write no                                      | otes on                                                                                              |

|          | (i)                                           | Channel length modulation & Mobility variation (8)                                                   |

|          | (ii)                                          | MOS models & tristate inverter (8)                                                                   |

|          | (22)                                          | UNIT-III                                                                                             |

| 1        | (i)                                           |                                                                                                      |

| 1        |                                               | Give a Verilog structural gate level description of 2-bit magnitude comparator. (10)                 |

|          | (ii)                                          | Give a brief account of timing control and Gate delay in Verilog.                                    |

|          | (11)                                          | (6)                                                                                                  |

|          | ;<br>                                         | (0)                                                                                                  |

| 2        | Write no                                      | otes on                                                                                              |

| <u> </u> | + (i) VLS                                     | I Design flow. (8)                                                                                   |

|          |                                               | gn Hierarchy. (8)                                                                                    |

| 3        | (i)                                           | Explain about the switch primitives used in Verilog HDL                                              |

|          |                                               | (8)                                                                                                  |

|          | (ii)                                          | Write the behavioral and structural description of 4X1 MUX in Verilog                                |

|          |                                               | HDL. (8)                                                                                             |

| 4        | (i)                                           | Explain Behavioral RTL Modeling with an example. (8)                                                 |

|          | (ii)                                          | Explain switch level modeling with an example. (8)                                                   |

| 5        | (i)                                           | Construct CMOS 2-input NAND and NOR gate with required truth tables.                                 |

| _        |                                               | Write the verilog code using NMOS and PMOS primitives.(12)                                           |

|          | (ii)                                          | Explain how to model resistive elements and power supply in verilog                                  |

|          | (11)                                          | HDL.(4)                                                                                              |

| 6        | (i)                                           | Give a Verilog structural gate level description of a ripple carry adder.(10)                        |

|          | (ii)                                          | Write a brief note on the conditional statements available in Verilog. (6)                           |

| 7        | (i)                                           | Write Verilog code in structural and Behavioral modeling to describe the                             |

| •        |                                               | operation of a priority encoder(10)                                                                  |

|          | (ii)                                          | Write Verilog code in data flow model to describe the operation of equality                          |

|          | (11)                                          | detector. (6)                                                                                        |

| 8        | Explain o                                     | different types of operators in Verilog HDL with example(16)                                         |

| 9        | (i)                                           | Explain the number englification methodology with war 1 - 5 1                                        |

| ,        | (1)                                           | Explain the number specification methodology with examples for verilog HDL. (6)                      |

|          | (ii)                                          | Explain major capabilities of verilog HDL. (10)                                                      |

| 10       | (i)                                           | Describe the operation of D-FF in Behavioral Modeling. (6)                                           |

| 10       | (ii)                                          | Describe the operation of Full adder in data flow modeling. (6)                                      |

|          | (iii)                                         | Write notes on procedural assignments. (4)                                                           |

|          |                                               | UNIT-IV                                                                                              |

| 1        | (i)                                           | 7                                                                                                    |

| 1        | (ii)                                          | Draw the ASIC design flow and explain(8)  Draw the structure of Yiliny, Configurable Logic block (8) |

| 2        | <del>  `                               </del> | Draw the structure of Xilinx Configurable Logic block (8)                                            |

| 3        |                                               | he types of ASICs with neat diagram (16)                                                             |

| 4        |                                               | es on programmable logic devices. (16)                                                               |

| 5        | Explain the                                   | he architecture of reprogrammable gate array(16)                                                     |

| <u>)</u> | (1) W                                         | rite short notes on Antifuse and ViaLink (8)                                                         |

| Explain the chip level test techniques. (16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| (ii) Parallel scan(8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             |

| Write notes on (i) Partial Serial scan(8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9           |

| (ii) Explain how serial scan testing is implemented (8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 3           |

| What is IDDQ lesting? (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $\propto$   |

| Wh                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <del></del> |

| (i) Explain the SCOAP algorithm for assigning controllabilities &                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6           |

| Explain system level test techniques. (16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | S           |

| Explain the principles of Ad-hoc Testing, (16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4           |

| Explain self-test Techniques.(16)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | رى          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             |

| (i) Explain the different fault models (8)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2           |

| (ii) Name for (iii) Name for its in the control of |             |

| (1) What is the need for Testing? (4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | <u> </u>    |

| UNIT-V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -           |